PLL晶體振蕩器的優(yōu)點(diǎn)有哪些?

來(lái)源:http://taiheth.com 作者:泰河電子晶振 2019年05月07

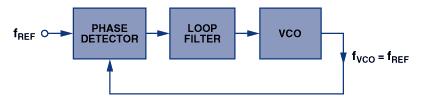

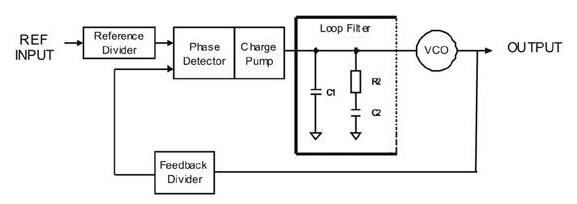

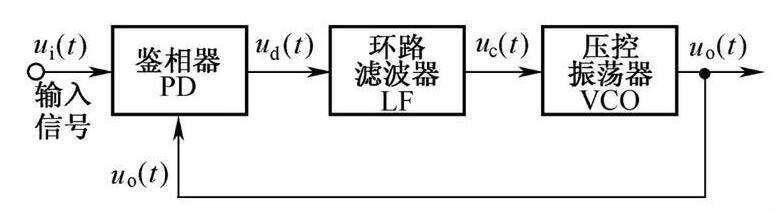

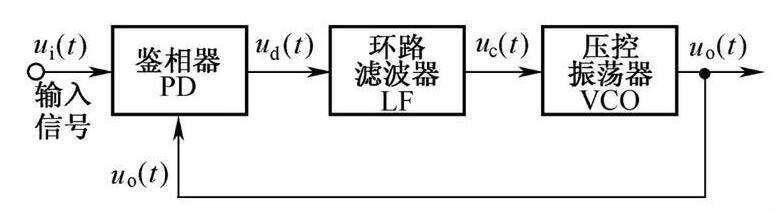

鎖相環(huán)(PLL)是電子設(shè)備中最早的反饋電路之一,在上個(gè)世紀(jì)70年代到80年代間,PLL已經(jīng)成為了定時(shí)電路的主要?jiǎng)恿Γ琍LL能夠與基頻同步,并將頻率乘以更高的值,從而提供靈活性和定時(shí)精度。并且對(duì)于PLL供應(yīng)商敏捷性的問(wèn)題給解決了商業(yè)周期帶來(lái)的挑戰(zhàn)。以及在高頻操作下可提高系統(tǒng)性能。我們來(lái)一起看一下對(duì)于PLL石英晶體振蕩器所帶來(lái)的優(yōu)點(diǎn)有哪些。

首先,任何石英晶體振蕩器的制造開(kāi)始都是從生長(zhǎng)和切割石英坯料的步驟開(kāi)始的。與之相關(guān)的需要較長(zhǎng)交期需要提前是不可以避免的,通常達(dá)到12-16周,如果不能準(zhǔn)確的知道所需要的振蕩器頻率就無(wú)法正常的開(kāi)始生產(chǎn)。每顆石英晶體振蕩器的制作都必須精確的切割每個(gè)毛坯以滿足最終頻率所需的尺寸。如果是生產(chǎn)周期長(zhǎng),則需要進(jìn)行分段和長(zhǎng)期的預(yù)測(cè)。在石英晶體工藝較長(zhǎng)的提前下是無(wú)法輕易處理預(yù)測(cè)誤差,突然上午需求或者輸出頻率要求的變化。

針對(duì)上面的那個(gè)問(wèn)題,在石英晶體振蕩器加入PLL之后便解決了這個(gè)問(wèn)題。通過(guò)使用PLL輸出頻率可以在制造過(guò)程結(jié)束時(shí)編程,與石英諧振頻一系列未編程的石英坯料來(lái)實(shí)現(xiàn)。這些坯料可以在幾周的短時(shí)間生產(chǎn)窗口內(nèi)解決大量需求或者頻率要求的變化。但在當(dāng)今瞬息萬(wàn)變的商業(yè)環(huán)境中,供應(yīng)鏈敏捷性可能意味著捕捉業(yè)務(wù)或者完全錯(cuò)過(guò)窗口之間的差異。

在高性能系統(tǒng)受益于更高頻率的參考時(shí)鐘,然而,石英晶體諧振器存在實(shí)際的頻率限制。專為更高頻率設(shè)計(jì)的空白,特別是250MHZ以上的空白。比標(biāo)準(zhǔn)的低頻技術(shù)要薄的很多。薄切坯料容易碎,難以在高產(chǎn)量下生產(chǎn),并且通常產(chǎn)量會(huì)比較低,另外,工作頻率高達(dá)1GHZ的石英坯料不能用當(dāng)今的技術(shù)制造。

現(xiàn)如今PLL的加入使得這些問(wèn)題得以解決,因?yàn)樗鼈兛梢詫⑹⒌幕l乘以任何值。在振蕩器中使用PLL可以使用標(biāo)準(zhǔn)石英技術(shù)生成高頻,避免使用薄切倒的臺(tái)面或者其它精品石英設(shè)計(jì)。這個(gè)沒(méi)有理論上的限制,它可以歸結(jié)為噪聲性能和功耗權(quán)衡。 但隨著硅電路的改進(jìn),PLL電路的頻率范圍,功耗和噪聲性能在通信和RF等高帶寬應(yīng)用中變得更具有吸引力。系統(tǒng)設(shè)計(jì)人員能夠在使用成熟的晶體技術(shù)的同時(shí),改善數(shù)據(jù)鏈路的完整性并降低高性能系統(tǒng)的誤碼率。現(xiàn)如今的許多時(shí)鐘電路都利用了PLL,與標(biāo)準(zhǔn)的晶體振蕩器相比,具有內(nèi)置PLL的石英晶體振蕩器具有擴(kuò)展的頻率范圍和更短的前置時(shí)間和可制造性。利用當(dāng)今先進(jìn)的PLL技術(shù),噪聲性能幾乎沒(méi)有任何折衷。沒(méi)有系統(tǒng)是完美的,甚至PLL也有一些缺點(diǎn)。在這種情況下,有兩個(gè)最突出。首先,PLL將其自身固有的噪聲引入時(shí)鐘信號(hào)。其次,每個(gè)PLL級(jí)消耗功率可能增加總功率要求并且通常也增加成本。然而基于PLL的振蕩器的好處通常可以克服其成本。

大多數(shù)的PLL電路的功耗隨著每一代而下降。滿足快速移動(dòng)業(yè)務(wù)周期和提高整體系統(tǒng)性能的供應(yīng)鏈敏捷性是使用基于PLL的石英晶體振蕩器的兩大優(yōu)勢(shì)。基于PLL的石英晶體振蕩器對(duì)噪聲和功率性能的影響極小,具有極佳的價(jià)值。在高性能系統(tǒng)中使用其它類型的振蕩器幾乎沒(méi)有其它別的理由。

針對(duì)上面的那個(gè)問(wèn)題,在石英晶體振蕩器加入PLL之后便解決了這個(gè)問(wèn)題。通過(guò)使用PLL輸出頻率可以在制造過(guò)程結(jié)束時(shí)編程,與石英諧振頻一系列未編程的石英坯料來(lái)實(shí)現(xiàn)。這些坯料可以在幾周的短時(shí)間生產(chǎn)窗口內(nèi)解決大量需求或者頻率要求的變化。但在當(dāng)今瞬息萬(wàn)變的商業(yè)環(huán)境中,供應(yīng)鏈敏捷性可能意味著捕捉業(yè)務(wù)或者完全錯(cuò)過(guò)窗口之間的差異。

在高性能系統(tǒng)受益于更高頻率的參考時(shí)鐘,然而,石英晶體諧振器存在實(shí)際的頻率限制。專為更高頻率設(shè)計(jì)的空白,特別是250MHZ以上的空白。比標(biāo)準(zhǔn)的低頻技術(shù)要薄的很多。薄切坯料容易碎,難以在高產(chǎn)量下生產(chǎn),并且通常產(chǎn)量會(huì)比較低,另外,工作頻率高達(dá)1GHZ的石英坯料不能用當(dāng)今的技術(shù)制造。

現(xiàn)如今PLL的加入使得這些問(wèn)題得以解決,因?yàn)樗鼈兛梢詫⑹⒌幕l乘以任何值。在振蕩器中使用PLL可以使用標(biāo)準(zhǔn)石英技術(shù)生成高頻,避免使用薄切倒的臺(tái)面或者其它精品石英設(shè)計(jì)。這個(gè)沒(méi)有理論上的限制,它可以歸結(jié)為噪聲性能和功耗權(quán)衡。 但隨著硅電路的改進(jìn),PLL電路的頻率范圍,功耗和噪聲性能在通信和RF等高帶寬應(yīng)用中變得更具有吸引力。系統(tǒng)設(shè)計(jì)人員能夠在使用成熟的晶體技術(shù)的同時(shí),改善數(shù)據(jù)鏈路的完整性并降低高性能系統(tǒng)的誤碼率。現(xiàn)如今的許多時(shí)鐘電路都利用了PLL,與標(biāo)準(zhǔn)的晶體振蕩器相比,具有內(nèi)置PLL的石英晶體振蕩器具有擴(kuò)展的頻率范圍和更短的前置時(shí)間和可制造性。利用當(dāng)今先進(jìn)的PLL技術(shù),噪聲性能幾乎沒(méi)有任何折衷。沒(méi)有系統(tǒng)是完美的,甚至PLL也有一些缺點(diǎn)。在這種情況下,有兩個(gè)最突出。首先,PLL將其自身固有的噪聲引入時(shí)鐘信號(hào)。其次,每個(gè)PLL級(jí)消耗功率可能增加總功率要求并且通常也增加成本。然而基于PLL的振蕩器的好處通常可以克服其成本。

大多數(shù)的PLL電路的功耗隨著每一代而下降。滿足快速移動(dòng)業(yè)務(wù)周期和提高整體系統(tǒng)性能的供應(yīng)鏈敏捷性是使用基于PLL的石英晶體振蕩器的兩大優(yōu)勢(shì)。基于PLL的石英晶體振蕩器對(duì)噪聲和功率性能的影響極小,具有極佳的價(jià)值。在高性能系統(tǒng)中使用其它類型的振蕩器幾乎沒(méi)有其它別的理由。

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2023-07-12]康納溫菲爾德推出符合Stratum3E...

- [2023-06-26]選擇石英晶體要了解的必要參數(shù),...

- [2023-06-25]艾伯康公司發(fā)布連續(xù)電壓有源晶振...

- [2021-01-18]今日主題:什么樣性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪惡化?都...

- [2020-12-09]干貨干貨!愛(ài)普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎樣的,這...

- [2020-09-01]Oscillator的制造流程究竟是怎樣...